Hochrechnung

Fall Kodik: Sony bittet Activision Blizzard nach Ermittlungen durch das Wall...

Laut der E-Mail sagten sich Jim Ryan und andere Führungskräfte von PlayStation: „Bescheiden und offensichtlich fassungslos"Mit den angekündigten Informationen Das Wall Street Journal, Activision...

Tech

Es kommt in den USA an, aber in Frankreich müssen wir noch warten

Acht US-Bundesstaaten haben gerade angekündigt, dass sie in...

The Elder Scrolls 6 Teasé für Xbox

Scheichrollen 6 Das Erscheinungsdatum mag Jahre entfernt sein, aber es hört nicht...

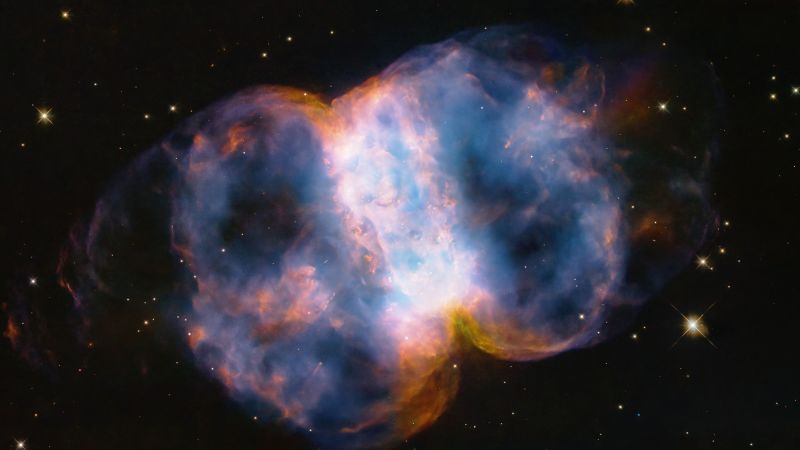

Die NASA enthüllt das tiefste Bild des Universums, das jemals gemacht wurde

Es ist ein erstaunliches...

ECONOMY

Covid trifft taiwanesische Chipfabriken

Kathryn Hill

Taipeh / 09.06.2021 02:35:15

...

Die ersten Runden im Wasser des größten Liners der Welt

Vor Saint-Nazaire hat Marvel of the Seas am Freitag, den 20. August, zum ersten Mal das Meer gekostet, ein Ausflug, der Teil einer Reihe...

Kanada will Internetriesen dazu zwingen, Mediengelder zu zahlen

Während mehr als 450 kanadische Nachrichtenagenturen seit 2008 ihre Türen geschlossen haben, will die Regierung Journalisten für die Ausstrahlung ihrer Inhalte bezahlen.

...

Ein Tag und eine Nacht im Picasso-Museum an diesem Wochenende für einen beispiellosen und...

Bei Tag und Nacht entdecken CelestineUnd Matador Und Musiker wo Küsse : Einige der größten Werke von Pablo Picasso werden samstags und sonntags rund...

ENTERTAINMENT

Am Montag, den 12. April, beginnen die Kämpfe bei „La Voz Kids“.

Camilo, Belinda, Maria Jose, Mao und Ricky haben...

Rihanna und A$AP Rocky kommen von einem Nachtclub-Türsteher wieder zusammen

Die Wache wusste nicht, wer sie warenDie Sequenz sorgte an diesem Donnerstag in den sozialen Medien für Aufruhr. Ein im Internet kursierendes...

Großer Schreck! Polina Goto prangert schreckliche Erfahrungen mit einem Uber-Fahrer an

mexikanische schauspielerin Paulina Guto Er gab an, dass er einen sehr unangenehmen Moment hatte, als er ein Taxi vom Bahnsteig nahm ÜberDies liegt daran,...

Louis Bertignac verliebte sich beim Cabourg Festival in Zoe Adjani und Alice Blaydy

Cabourg ist die Outdoor-Plattform für die Starparade! Norman veranstaltet eine neue Ausgabe seines Filmfestivals. Louis Bertignac und seine Partnerin Letitia Brichet, Zoe...

Barney-Film: „Black Panther“ Daniel Kaluuya erklärt, warum er den Film nach dem Marvel-Erfolg machen...

Barney und seine Freunde Sie wird direkt im Kino arbeiten und Kinder, die mit ihren Abenteuern aufgewachsen sind, werden von den Neuigkeiten nicht mehr...

SCIENCE

Diese entzückende springende Spinne kann ihre eigene lebendigste Farbe nicht wirklich...

Springspinnen mögen außergewöhnliche Augen haben, aber eine entzückende Art scheint einen merkwürdigen Mangel an Sehvermögen zu haben. Neue experimentelle Beweise deuten darauf hin,...

NEUESTE ARTIKEL

Latest article

Experten betrachten Trumps Prozess mit Argwohn

StartseitePolitikStand: 26. April 2024, 13:55 Uhraus: Fabian MüllerEr drücktTeiltDerzeit laufen in den USA mehrere Prozesse gegen Donald Trump. Anwälte gehen davon aus, dass...

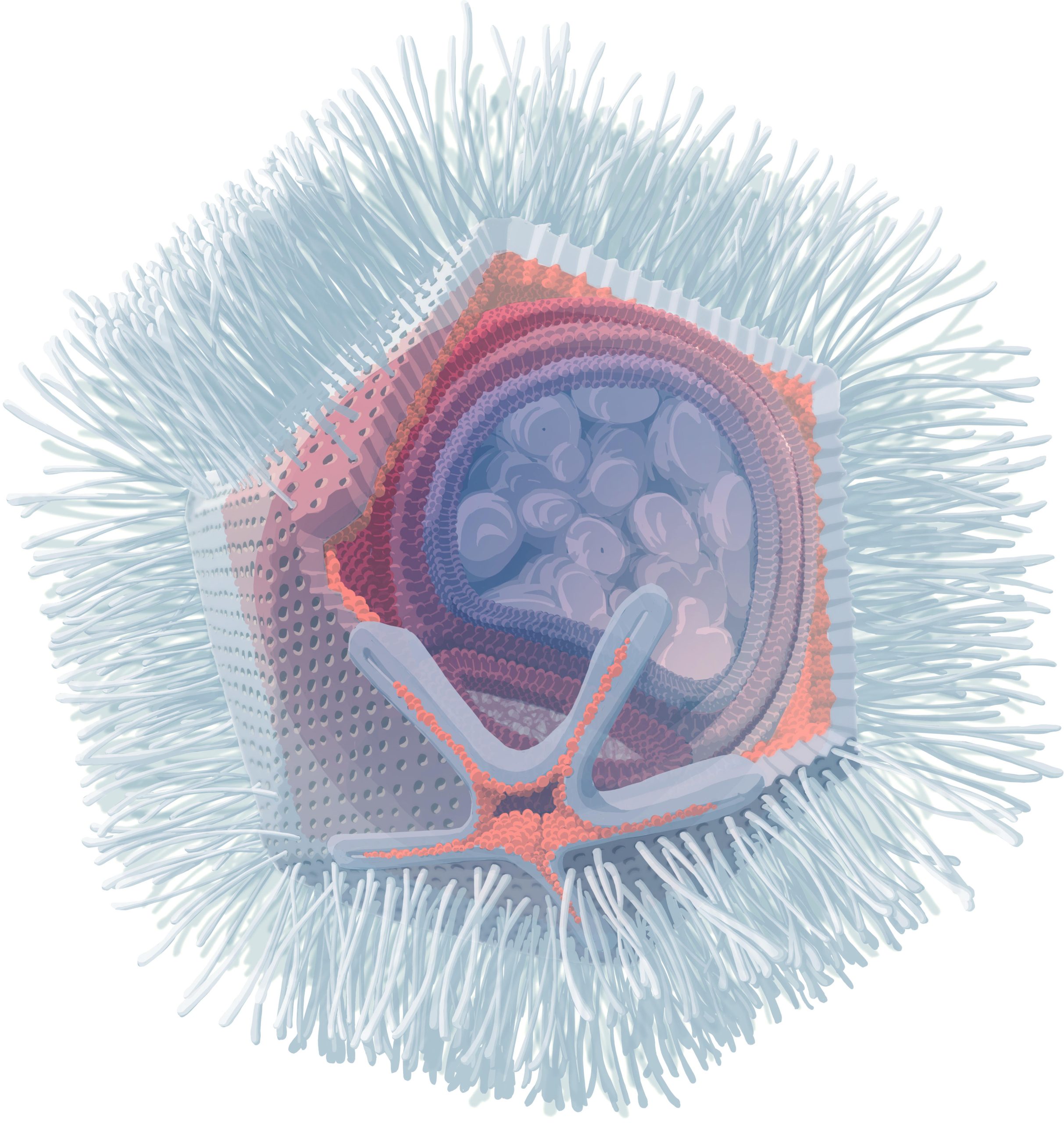

Ungewöhnliches Riesenvirus in Österreich entdeckt

Forscher der Universität Wien haben Viren namens Naegleriavirus entdeckt, die das gefährliche Bakterium Naegleria fowleri infizieren und neue Einblicke in die Virusbiologie und mögliche...

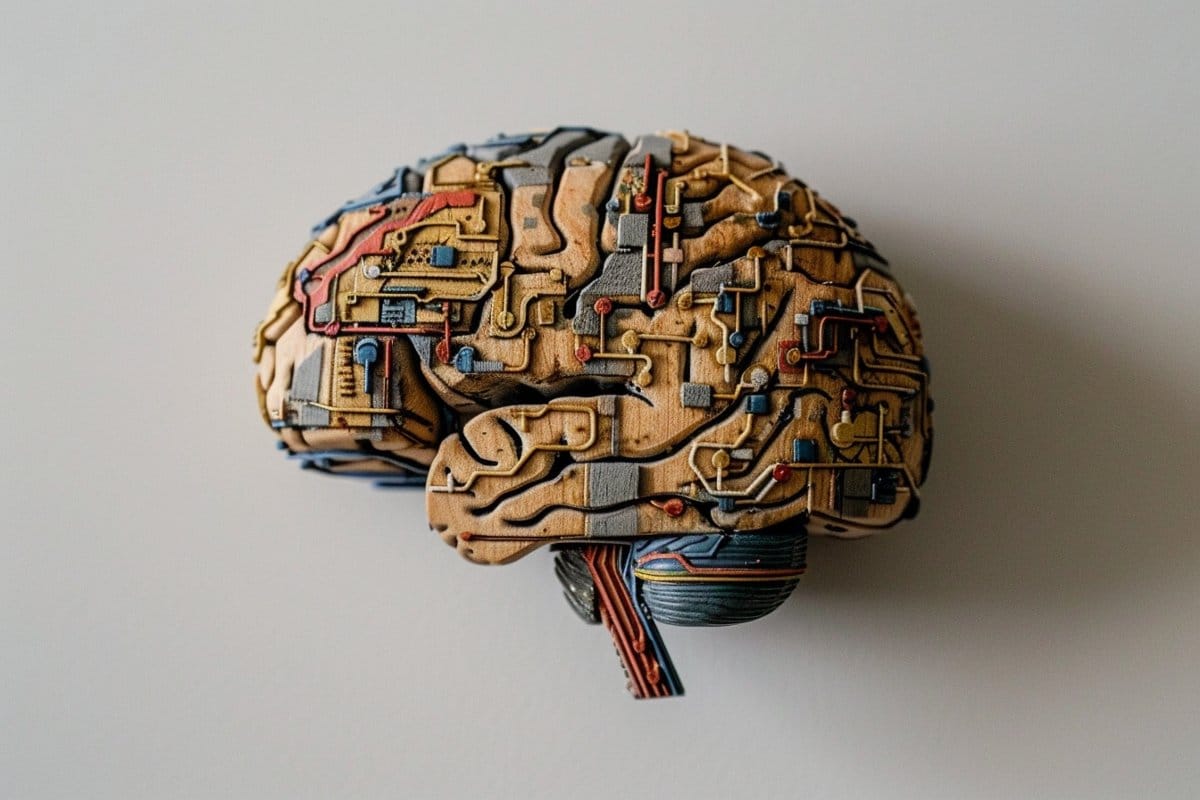

Aktualitäts- und zentrale Tendenzverzerrungen hängen mit dem Arbeitsgedächtnis zusammen

Zusammenfassung: Der Aktualitätsbias im Arbeitsgedächtnis ist untrennbar mit dem zentralen Tendenzbias verbunden und bietet eine einheitliche Erklärung für diese weitreichenden kognitiven Phänomene. Die...