Hochrechnung

Tech

5 Android-Apps zum sofortigen Entfernen! Rausfinden …

Wie wir wissen, ist Android OS eines der bedrohlichsten Betriebssysteme, wenn es um Malware geht. Trotz aller Bemühungen ist Google immer noch nicht...

Nintendo Switch bekommt eine etwas eingeschränkte Twitch-App

Kurzum: Twitch hat diese Woche eine native App für die Nintendo Switch veröffentlicht. Der Dienst lässt sich jedoch nicht in die Plattform sowie...

Moderne Technologien mit großem Potenzial – diese Innovationen verändern unsere Gesellschaft

Ein Leben ohne Technik? In unserer modernen Gesellschaft ist dieser Gedanke unvorstellbar, denn digitale Innovationen bestimmen unseren Alltag. Allerdings gibt es inzwischen so viele...

ECONOMY

Covid trifft taiwanesische Chipfabriken

Kathryn Hill

Taipeh / 09.06.2021 02:35:15

...

Amazon unternimmt Schritte, um Weihnachtsverzögerungen zu vermeiden

Amazon.com Inc. fördert. für die Größe seiner Logistikaktivitäten, um die öffentliche Besorgnis zu zerstreuen, dass die Lieferkettenkrise das Weihnachtsgeschäft beeinträchtigen könnte.Risiko, weniger Mitarbeiter...

Die Europäische Handelsbank muss möglicherweise handeln, wenn die Energiepreiserhöhungen konsequenter sind: Schnabel

(.)FRANKFURT (Reuters) – Höhere Energiepreise könnten die Europäische Zentralbank dazu zwingen, bei steigender Inflation nicht mehr nach Unsicherheit zu suchen und an einer moderaten...

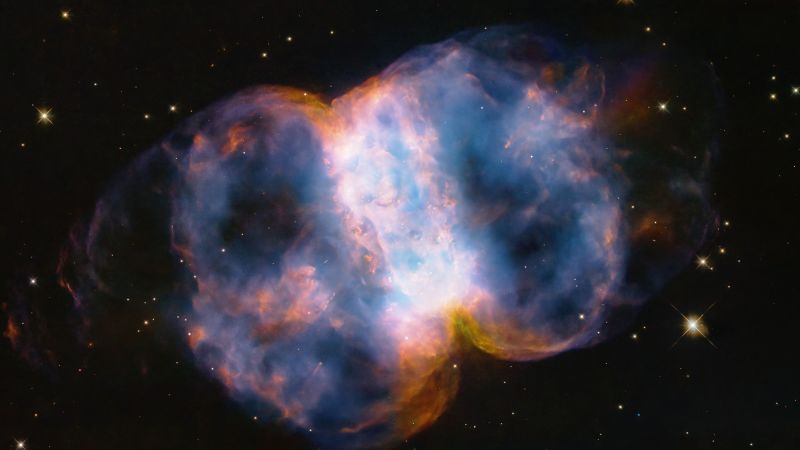

Die Orion-Kapsel der NASA umkreist den Mond und fängt Ansichten ein, die einem schwindelig...

Eine von einer Kamera auf einem der Flügel des Orion-Sonnensystems aufgenommene Ansicht, die die Position der Erde unter dem Horizont des Mondes zeigt. ...

Beobachten Sie grüne Kometen und weitere Weltraum- und Astronomieereignisse im Februar

grünes Licht für einen KometenDer Komet C/2022 E3 (ZTF) hat sich zum ersten Mal seit etwa 50.000 Jahren stetig der Erde genähert. Am...

Kriminalität: Neue Insassen im „am meisten kritisierten Gefängnis der Welt“

DREl Salvadors Regierung hat weitere 2.000 mutmaßliche Bandenmitglieder in ein riesiges neues Gefängnis verlegt – und erneut ein Video mit provokanten Bildern...

ENTERTAINMENT

Das London Film Festival kehrt im Oktober in die Kinos zurück

Foto: BFI

Die 65. Ausgabe des Wettbewerbs zeigt in der britischen Hauptstadt 159 Filme aus aller Welt, darunter 21 Weltpremieren sowie Dokumentationen, Kurzfilme und Animationen.

Esther Exposito hat dieses Wochenende mit ihrer bezaubernden Persönlichkeit gerockt

Seit er berühmt wurde, Ester Exposito Sie wurde eine der einflussreichsten Schauspielerinnen der Show. Ihre Schönheit und ihr Talent für die Schauspielerei machten...

Pride March: Welche Route ist an diesem Samstag in Paris geplant?

Am Samstag, den 25. Juni, werden fast 500.000 Menschen auf die Straßen von Paris gehen, um an der Pride Parade teilzunehmen. Suchen Sie...

A&E-Premiere Kisstory, der Fall und die Auferstehung eines Kusses

Guadalajara, Galle, 21. August 2021. Die Wartezeit für die Fans der Kiss-Gruppe hat ein Ende, mit der lateinamerikanischen Premiere von Kisstory, die am Samstag,...

SCIENCE

Israel meldet seltene Doppelinfektion mit COVID-19 und Influenza

Abonnieren Sie unsere Seite Sonderausgabe Newsletter Für ein tägliches Update zur Coronavirus-Pandemie.

Eine fragwürdige Unterscheidung einer ungeimpften schwangeren israelischen Frau ist, dass sie den ersten...

NEUESTE ARTIKEL

Latest article

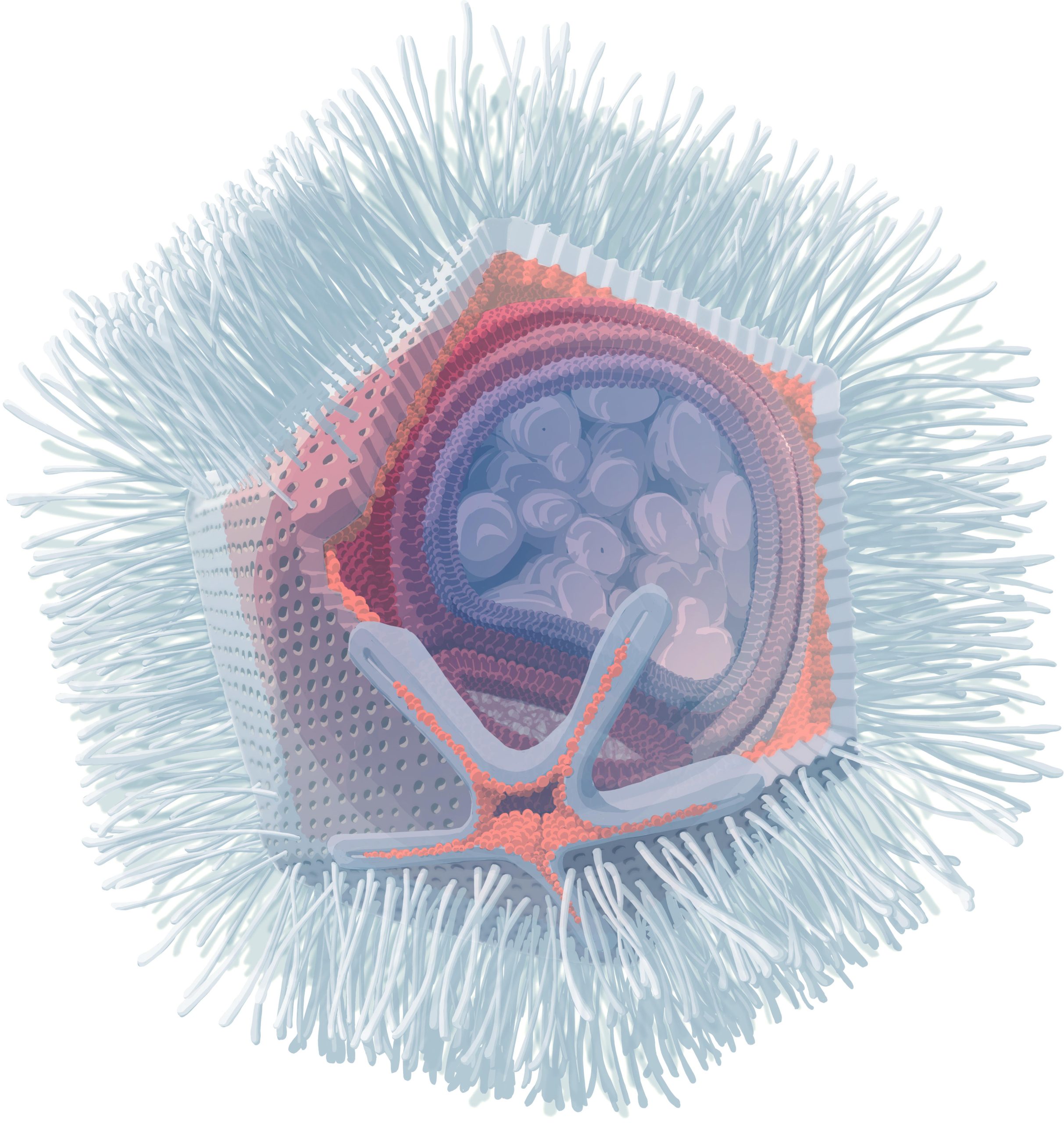

Ungewöhnliches Riesenvirus in Österreich entdeckt

Forscher der Universität Wien haben Viren namens Naegleriavirus entdeckt, die das gefährliche Bakterium Naegleria fowleri infizieren und neue Einblicke in die Virusbiologie und mögliche...

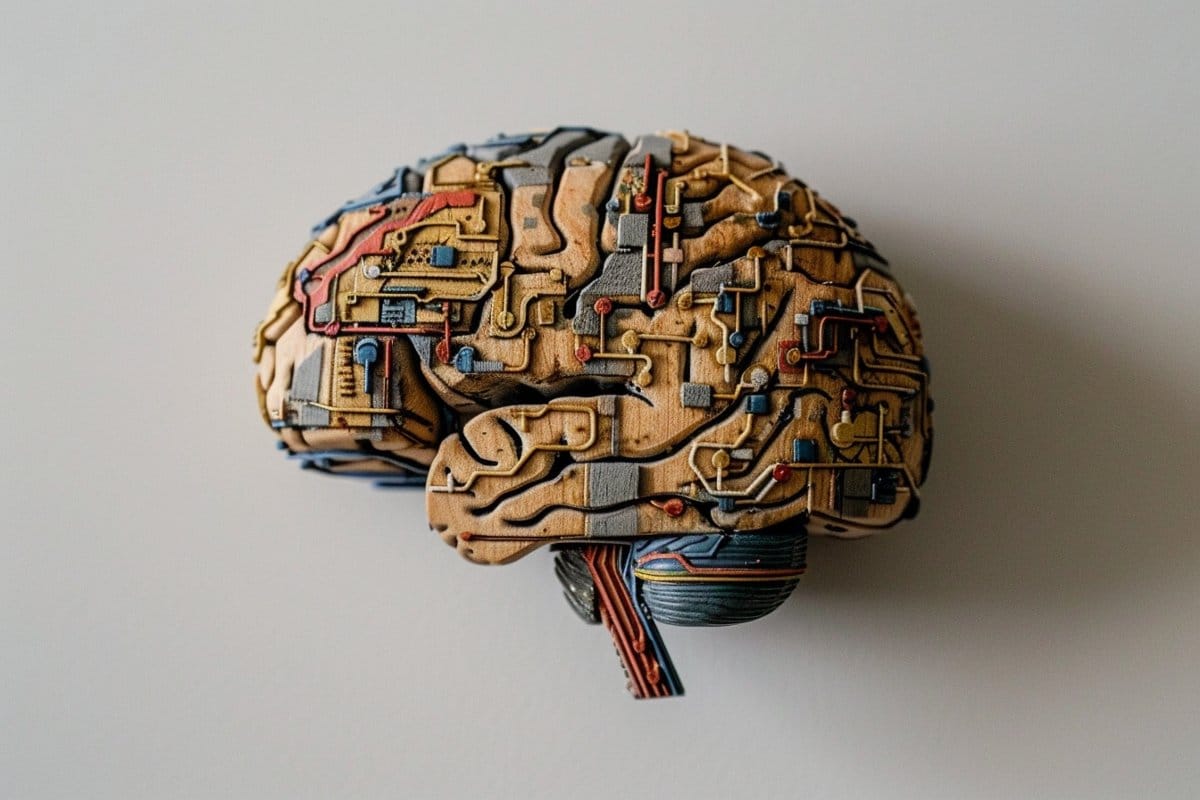

Aktualitäts- und zentrale Tendenzverzerrungen hängen mit dem Arbeitsgedächtnis zusammen

Zusammenfassung: Der Aktualitätsbias im Arbeitsgedächtnis ist untrennbar mit dem zentralen Tendenzbias verbunden und bietet eine einheitliche Erklärung für diese weitreichenden kognitiven Phänomene. Die...